CXL(Compute Express Link)�����,是一种全新的装备互联手艺标准�����,已成为业界突破内存瓶颈的存储新手艺��。不但用于内存容量/带宽扩展�����,还用于异构互联�����,数据中心资源池解耦��。在数据中心�����,CXL手艺可以将差别的盘算和存储资源举行互联�����,用更高的系统性能和效率来解决数据中心内存问题��。

CXL手艺的泛起

云盘算、大数据剖析、人工智能、机械学习等应用的快速生长带来数据中心存储和处置惩罚数据需求的爆炸性增添��。古板DDR内存接口保存总带宽、每焦点平均带宽和容量可扩展性受限等问题��。尤其在数据中心�����,受限于大宗内存问题�����,新的内存接口手艺CXL泛起��。

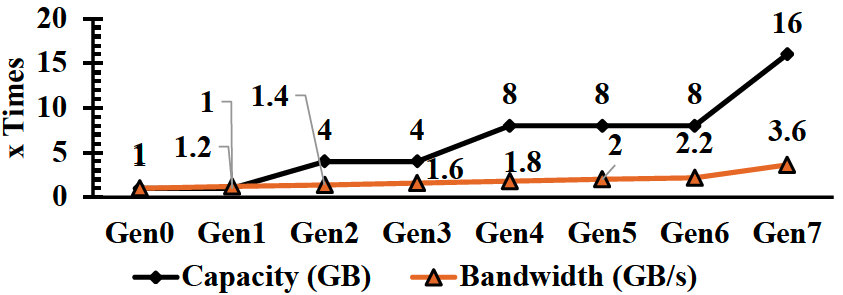

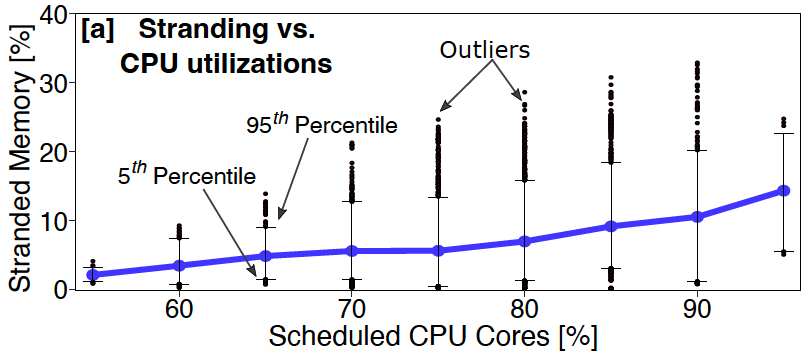

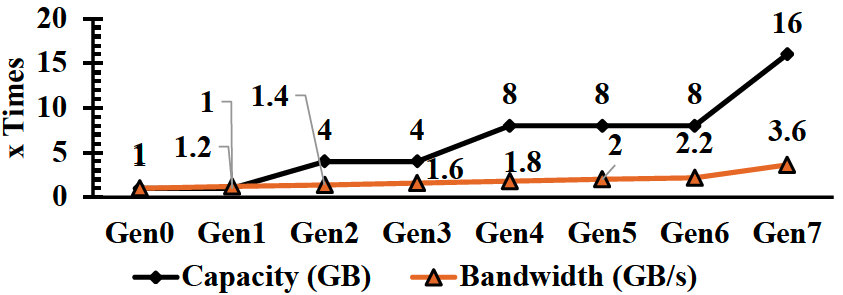

在数据中心�����,CPU内存是紧耦合关系�����,每代CPU都接纳新的内存手艺实现更高的容量和带宽��。自2012年以来�����,焦点数目迅速增添�����,但每个内核的内存带宽和容量并未响应增添�����,反而下降��。这种趋势将在未来继续�����,内存容量增添速率也快于内存带宽�����,这对系统性能影响重大��。

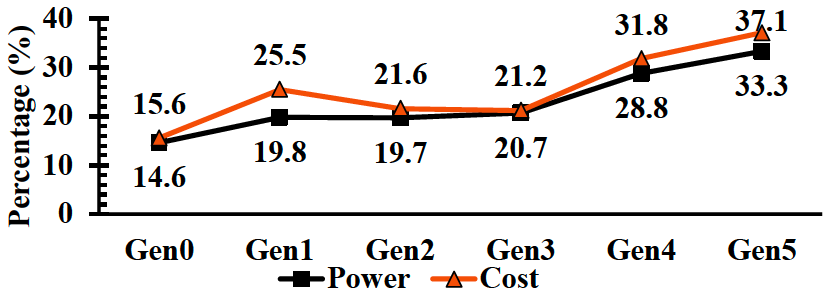

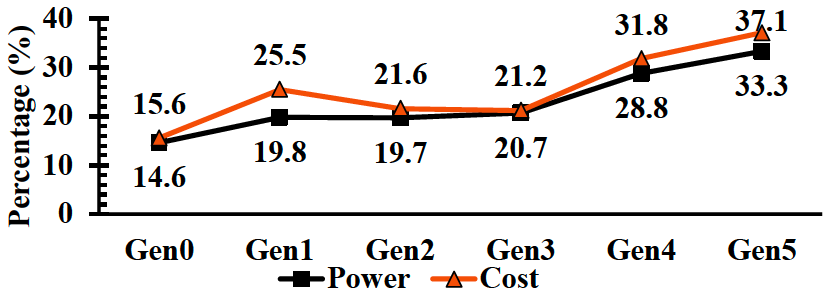

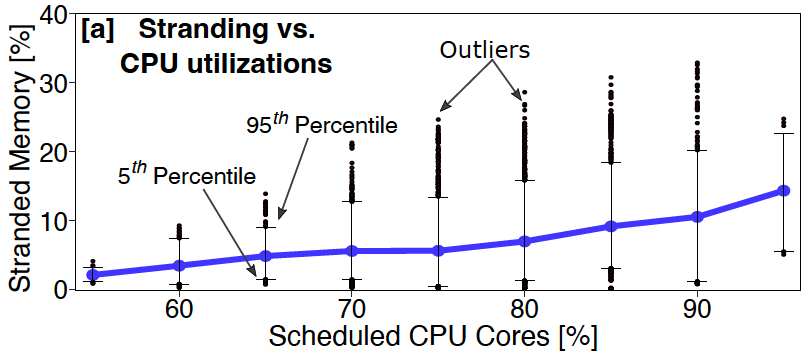

别的�����,直连DRAM和SSD在延迟和本钱方面的重大差别�����,使得腾贵的内存资源往往使用率很低�����,过失的盘算和内存比例很容易造成内存闲置(Stranded)租不出去的征象��。数据中心营业作为全球资源最麋集的行业之一�����,低使用率是一个很大的肩负��。微软体现�����,50%的效劳器总成原来自DRAM��。只管DRAM本钱很高�����,但25%的DRAM内存照旧铺张了��。下图来自Meta内部的统计数据也显示类似征象��。内存本钱占系统总本钱的比例现实上在一直上升�����,系统的主要本钱已经酿成是内存而不是CPU自己�����,使用CXL内存资源池可以有用改善这一问题�����,通过给系统动态分派内存资源可以优化盘算和内存比例关系优化TCO��。

差别内存手艺的延迟概况

内存带宽/容量随时间推移增添

差别代内保存机架TCO/功耗占比

Microsoft Azure内存闲置

基于古板内存问题�����,业界一直在追求接纳新的内存接口手艺和系统架构��。

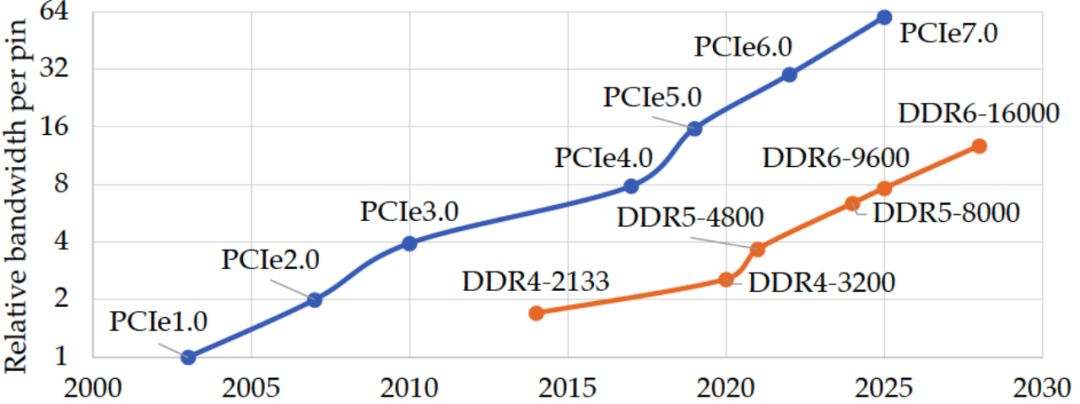

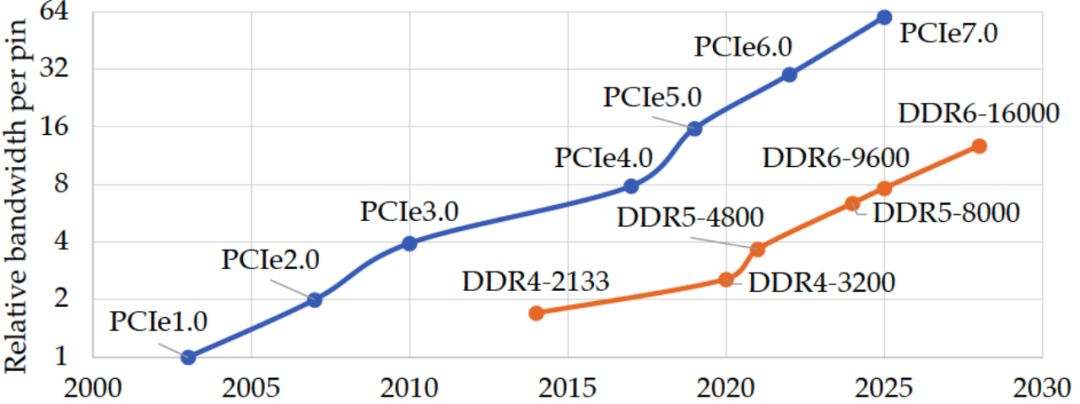

在内存接口手艺方面�����,PCI-Express(peripheral component interconnect express)成为首选��。PCIe是串行总线�����,使用PCIe从性能和软件的角度来看差别装备之间通讯的开销相对较高�����,但好新闻是�����,PCIe将凭证妄想在2023年底完成7.0版的批准�����,提供高达256GB/s 的速率���;这距离16 GT/s速率的4.0版PCIe问世还不到两年��。加速PCIe生长蓝图的主要推手是云端运算需求���;而PCIe以往是每3~4年�����,甚至是7年会将数据传输速率提升一倍��。

PCIe vs DDR 带宽比照

系统架构则是历经几代进化更迭��。最初为实现多个效劳器共享资源池的实验�����,通常使用RDMA手艺在通用以太网或InfiniBand上面实现�����,这些通讯要领通常时延更高(外地内存几十纳秒vsRDMA几个微秒)和更低的带宽�����,并且也无法提供内存一致性等要害功效��。

在40Gbps链路带宽网络可实现的往返延迟(总计)

以及导致往返延迟增添的组件(使用100Gbps可将数据传送镌汰0.5us)

2010年�����,CCIX成为潜在的行业标准��。它的驱动因素是需要比目今可用手艺更快的互连�����,并且需要缓存一致性�����,以便在异构多处置惩罚器系统中更快地会见内存��。CCIX规范的最大优势是它建设在PCI Express规范的基础之上�����,但它因缺乏要害行业支持�����,从未真正腾飞��。

而CXL依托现有的PCIe5.0的物理层和电气层标准及生态系统�����,为内存加载/存储(load/Store)事务增添缓存一致性和低时延特征��。由于建设了行业中大大都主要加入者都支持的行业标准协议�����,CXL使向异构盘算的过渡成为可能并获得普遍的业界支持��。AMD的Genoa和Intel的SapphireRapids将在2022年尾/2023年头支持CXL1.1��。至此�����,CXL成为业界和学术界最有前途解决这一问题的手艺之一��。

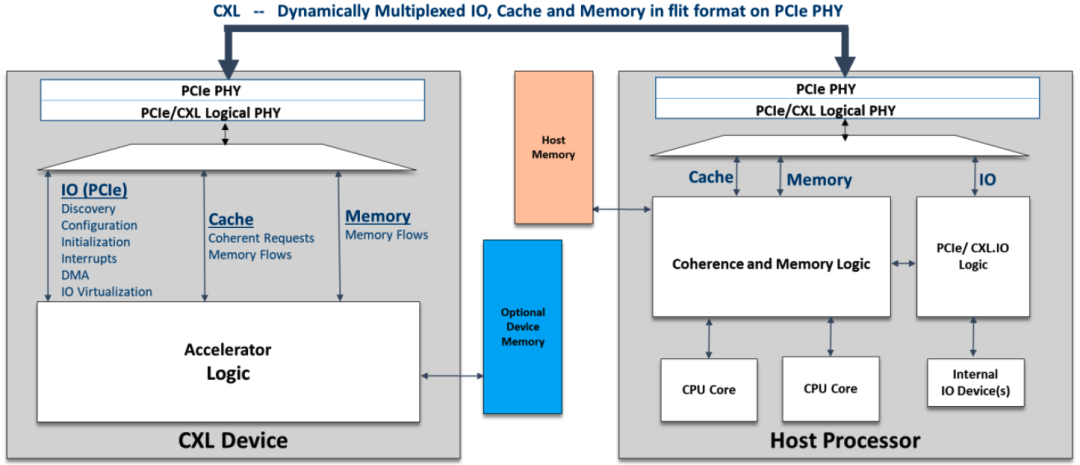

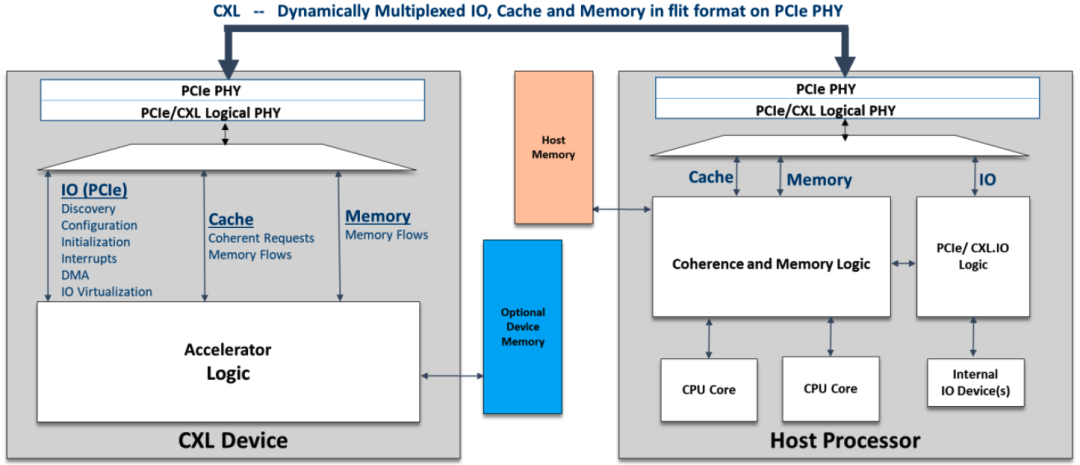

CXL构建在PCIe物理层上�����,具备现有PCIe物理及电气接口特征�����,提供高带宽�����,高可扩展性特点��。另外CXL与古板的PCIExpress(PCIe)互连相比具有更低的时延�����,并且还提供一组奇异的新功效使CPU能够以具有加载/存储(load/store)语义的高速缓存一致(Cache-Coherent)方法与外围装备(内存扩展和加速器及其毗连的存储器)通讯��。该手艺坚持CPU内存空间和附加装备上内存的一致性�����,允许资源共享�����,从而获得更高性能�����,降低软件栈重大性��。与内存相关的装备扩展是CXL主要目的场景之一��。

CXL依托现有PCIe物理及电气接口特征

CXL/PCIe实现内存资源扩展/池

CXL手艺的原理

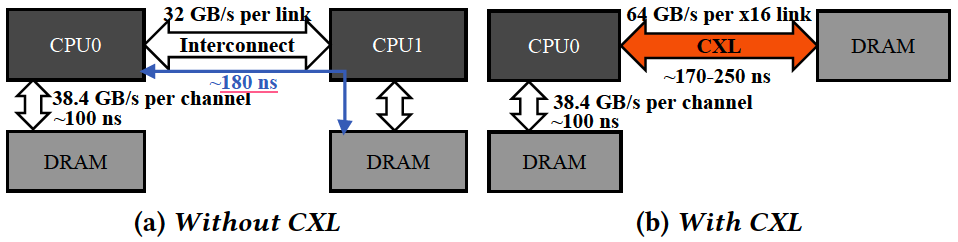

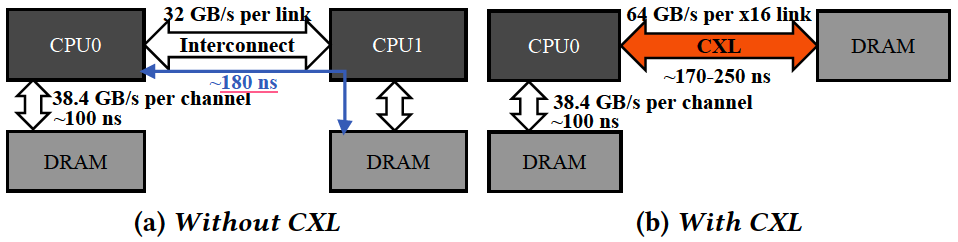

CXL现实上包括三种协议�����,但并非所有协议都是延迟的灵丹妙药��。CXL.io(运行在PCIe总线的物理层上)仍然具有与以往相同类型的延迟�����,但其他两个协议�����,CXL.cache和CXL.mem接纳磷泣快的路径�����,镌汰了延迟��。大大都CXL内存控制器会增约莫100-200纳秒的延迟�����,特另外重准时器会增添或破费几十纳秒�����,详细取决于装备与CPU的距离��。

CXL引入时延与NUMA靠近

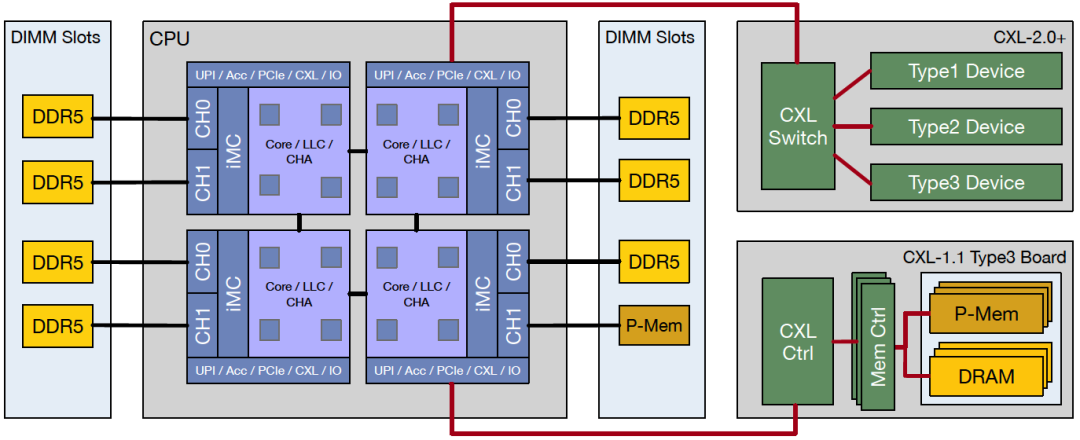

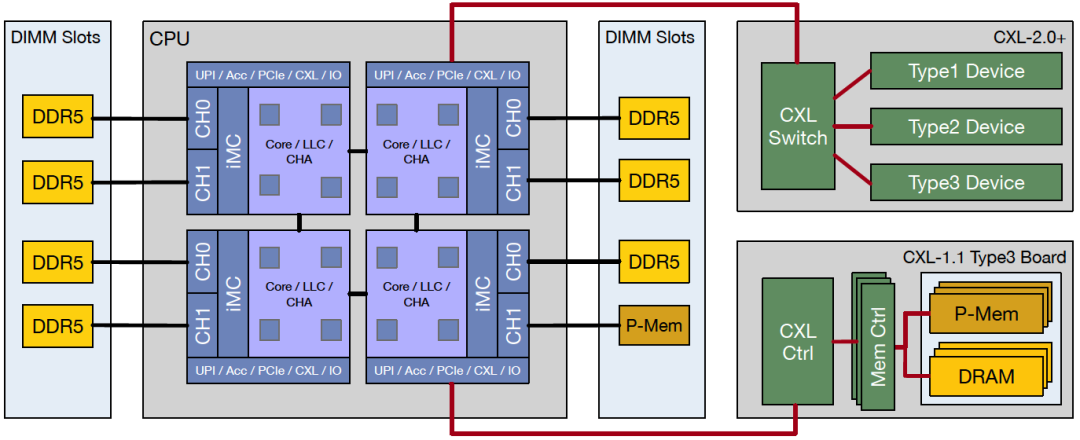

CXL/PCIe扩展内存系统架构

CXL在PCIePHY层复用差别的协议�����,CXL1.0/1.1规范附带3个协议支持-CXL.io、CXL.cache和CXL.mem�����,大大都CXL装备将使用CXL.io、CXL.cache和CXL.mem的组合��。CXL.io 使用与 PCIe 相同的事务层数据包 (Transaction Layer Packet, TLP)和数据链路层数据包 (DLLP)��。TLP/DLLP笼罩在CXL flit的有用负载部分上��。CXL界说了跨差别协议栈提供所需效劳质量(QoS)的战略��。PHY级别的协议复用可确保CXL.cache和CXL.memory等延迟敏感协议具有与本机CPU到CPU对称一致性链路相同的低延迟��。CXL为这些延迟敏感协议界说了引脚到引脚响应时间的上限�����,以确保平台性能不会因实现一致性和内存语义的差别装备之间的延迟差别较大而受到倒运影响��。

- CXL.io可以被以为是标准PCIe的一个类似但刷新的版本��。

是用于初始化、链接、装备发明和枚举以及注册会见的协议��。它为I/O装备提供接口�����,类似于PCIeGen5��。CXL装备也必需支持CXL.io��。

- CXL.cache是界说主机(通常是CPU)和装备(例如CXL内存�����?榛蚣铀倨鳎┲浣换サ男��。

由于清静使用其外地副本�����,CXL.cache允许CXL装备连贯地会见缓和存主机CPU的内存�����,可以把这想象成一个GPU直接从CPU的内存中缓存数据��。

- CXL.mem是为主机处置惩罚器(通常是CPU)提供使用加载/存储下令直接会见装备附加内存的协议��。

允许主机CPU连贯地会见装备的内存�����,将此视为CPU使用专用存储级内存装备或使用GPU/加速器设惫亓内存��。

从左向右依次是CXLType1、CXLType3、CXLType2

CXL 2.0增添了对内存池和CXL交流的支持�����,允许众多主机和装备所有链接并相互通讯�����,从而使毗连在CXL网络上的装备数目显着增添��。多台主机可以毗连到交流机�����,然后将交流机毗连到种种装备�����,若是该CXL装备是多头的并毗连到多个主机的根端口�����,则也可以在没有交流机的情形下实现��。SLD(单个逻辑装备)是单个主机划分使用差别内存池�����,MLD(多个逻辑装备)旨在耦合多个主机以分享统一物理内存池��。

漫衍式内存资源网络将由结构治理器(FabricManager)认真分派内存及装备编排�����,它相当于控制平面或协调器�����,位于单独的芯片上或交流机中�����,通常不需要高性能�����,由于不接触数据面��。结构治理器(FabricManager)提供用于控制和治理该系统的标准API�����,可以实现细粒度的资源分派、热插拔和动态扩容允许硬件在各个主机之间动态分派和转移�����,无需任何重启��。将所有这些团结在一起�����,微软报告显示接纳CXL方法实现内存资源池整体可镌汰10%内存需求�����,进而降低5%的总效劳器本钱的潜力��。

CXL 2.0内存资源池(Switch vs Directconnect模式)

CXL手艺的生长

CXL生长势头强劲�����,三星、SK海力士、Marvell、Rambus、三星、AMD等大厂们的结构也在一直加速��。公有云供应商在内的所有超大规模企业都最先实验依赖CXL毗连内存池来改善内存闲置�����,动态无邪增添带宽和容量的问题��。但目今没有太多用于APP使用外地/外部混淆资源池的多级内存调理治理监控手艺�����,因此云效劳商若是刻意大规模使用基于CXL手艺的资源池系统�����,要么自己建�����,要么得寻找合适的系统软硬件供应商��。这方面微软、Meta等主要云效劳商已经走到前面��。

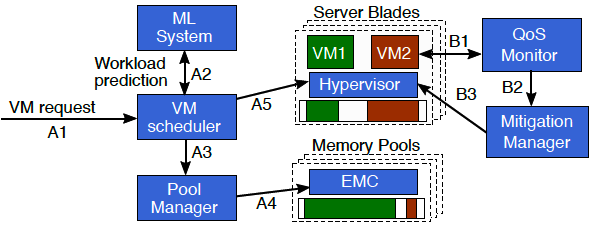

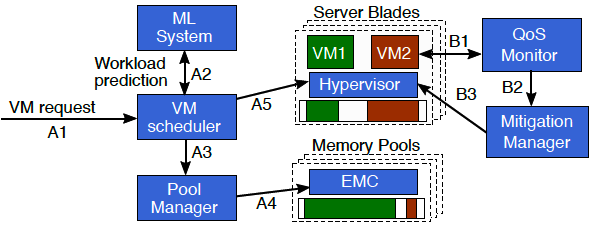

微软的Pond计划使用机械学习判断剖析虚机是否是时延敏感以及不被使用的额(untouched)内存巨细�����,并由此来判断调理VM在合适的外地或CXL远端内存位置�����,配合性能监控系统一直调解迁徙��。

微软Pond计划控制平面事情流程

(A) 的VM 调理程序使用基于 ML 的展望来识别延迟敏感的虚拟机及其可能未触及的内存量决议虚拟机的安排

(B) 监控若是效劳质量 (QoS) 不知足�����,调理迁徙控制治理器(Mitigation Manager)会重新设置虚拟机

作为智算中心网络建设者�����,PP电子5金狮网络致力于为客户提供立异的产品计划和效劳�����,推动行业生长和立异�����,让客户与未来更细密地毗连��。PP电子5金狮网络将一连立异�����,引领智算时代的网络生长潮流��。

参考文献:

TPP: Transparent Page Placement for CXL-Enabled Tiered-Memory

Pond: CXL-Based Memory Pooling Systems for Cloud Platforms

Demystifying CXL Memory with Genuine CXL-Ready Systems and Devices

Compute Express Link™ Specification 3.0 whitepaper

Design and Analysis of CXL Performance Models for Tightly-Coupled Heterogeneous Computing

Memory Disaggregation: Advances and Open Challenges

Network Requirements for Resource Disaggregation

A Case for CXL-Centric Server Processors